# **RDA012M4**

# 12 Bit 1.3 GS/s 4:1 MUXDAC

## Features

- ♦ 12 Bit Resolution

- 1.3 GS/s Sampling Rate

- 4:1 Input Multiplexer

- Master-Slave Operation for Synchronous Operation of Multiple Devices

- Differential Analog Output

- Input code format: Offset Binary

- Output Swing: 600 mV with 50 Ω Termination

- 3.3V NMOS-Compatible Data Inputs

- Differential ECL or Sinusoidal Clock Input

- LVDS Compatible Clock Output

- 10-bit static linearity

- Reference Output/Input Pin for Accurate Full-Scale Adjustment.

- 3.3V and -5.2V Power Supply

- 77 Lead HSD package

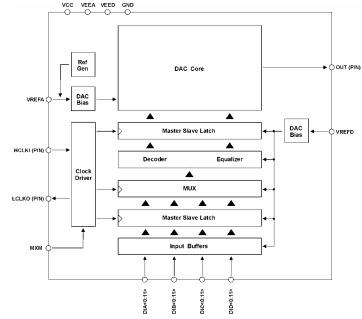

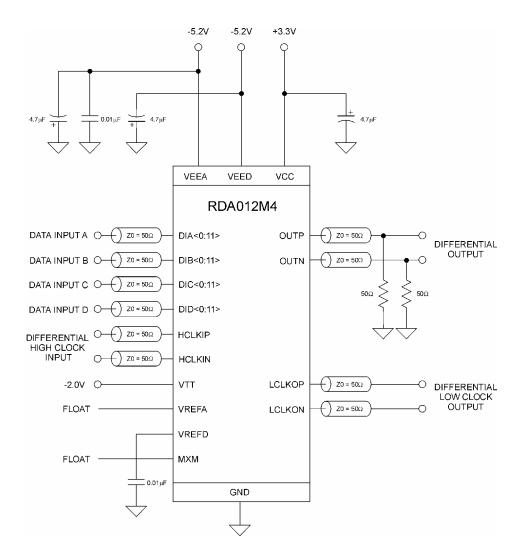

#### Figure 1 - Functional Block Diagram

## **Product Description**

The RDA012M4 is a digital-to-analog converter (DAC) with a 4:1 input multiplexer and a maximum update rate of 1.3GS/s. The integrated DAC utilizes a segmented current source to reduce the glitch energy and to achieve high linearity performance. For best dynamic performance, the DAC outputs are

internally terminated with  $50\Omega$  resistance, and outputs a nominal full-scale current of 12mA when terminated with external  $50\Omega$  resistors. For a convenient interface with most CMOS ICs, the digital data inputs are low voltage NMOS compatible.

## Ordering information

| PART NUMBER   | DESCRIPTION                             |

|---------------|-----------------------------------------|

| RDA012M4-DI   | 12 BIT 4:1 MUX 1.3GS/s DAC, DIE         |

| RDA012M4-HD   | 12 BIT 4:1 MUX 1.3GS/s DAC, HSD Package |

| EVRDA012M4-HD | RDA012M4-HD Evaluation Board            |

# Absolute Maximum Ratings

### Supply Voltages

| Between GNDs                |               |

|-----------------------------|---------------|

| Between VCCs                |               |

| VCCs to GND                 | 0 V to +3.8 V |

|                             |               |

| RF Input Voltages           |               |

|                             | 0 V to VCC    |

|                             |               |

| <b>HS Digital Input Vol</b> | tages         |

|                             | 0 V to VCC    |

| <b>Output Termination</b>   | Voltages      |

|                             | D0 V to VCC   |

|                             |               |

#### Temperature

| Operating Temperature30 to +100 °C   |

|--------------------------------------|

| Case Temperature15 to +85 °C         |

| Junction Temperature +120 °C         |

| Lead, Soldering (10 Seconds) +220 °C |

| Storage40 to 125 °C                  |

# **Electrical Specification**

| PARAMETER                 | SYMBOL                 | CONDITIONS, NOTE                                                    | TEST LEVEL | MIN  | TYP  | MAX  | UNITS             |

|---------------------------|------------------------|---------------------------------------------------------------------|------------|------|------|------|-------------------|

| ACCURACY                  | •                      |                                                                     |            |      |      |      |                   |

| Differential Nonlinearity | DNL                    |                                                                     | 2          |      | ±2   |      | LSB               |

| Integral Nonlinearity     | INL                    |                                                                     | 2          |      | ±2.5 |      | LSB               |

| DYNAMIC PERFORMANCE       |                        |                                                                     |            |      |      |      |                   |

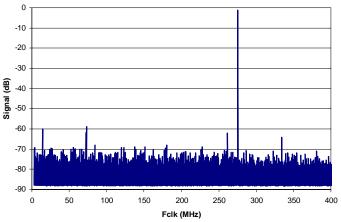

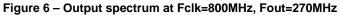

| Spurious Free Dynamic     | SFDR1                  | $F_{clk} = 800MHz$ , $F_{out} = 267MHz$                             | 1          |      | 56   |      | dBc               |

| Range                     | SFDR2                  | $F_{clk} = 1000MHz$ , $F_{out} = 333MHz$                            | 1          |      | 53   |      | dBc               |

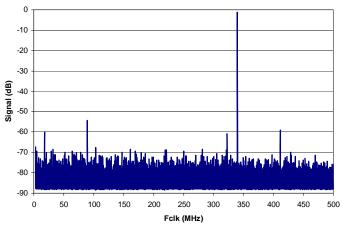

| Range                     | SFDR3                  | $F_{clk} = 1300MHz$ , $F_{out} = 400MHz$                            | 1          |      | 50   |      | dBc               |

| Signal Noise Ratio        | SNDR                   |                                                                     |            |      |      |      | dB                |

| Clock Feedthrough         | FD                     |                                                                     |            |      |      |      | dB                |

| ANALOG SIGNAL OUTPUT      | OUTP, OUT              | N)                                                                  |            |      |      |      |                   |

| Full-scale Output Range   | V <sub>FSS</sub>       | Single Ended, $50\Omega$ Termination to Ground                      | 2          | 570  | 600  | 630  | $mV_{p\text{-}p}$ |

| Full-scale Output Range   | V <sub>FSRS</sub>      | Single Ended, $50\Omega$ Termination to Ground (MIN=000h, MAX=FFFh) |            | -650 |      | 0    | mV                |

| Full-scale output swing   | V <sub>FSD</sub>       | Differential with $50\Omega$ Termination to Ground on each output   | 2          | 1140 | 1200 | 1260 | $mV_{p-p}$        |

| Output current            | I <sub>OUT</sub>       |                                                                     |            |      | 12   |      | mA                |

| Rise Time                 | T <sub>R,OUT</sub>     | 20%-80% with FSR output                                             |            |      |      |      | ps                |

| Fall Time                 | T <sub>F,OUT</sub>     | 20%-80% with FSR output                                             |            |      |      |      | ps                |

| Settling Time             | T <sub>SETTL</sub>     |                                                                     |            |      |      |      | ps                |

| CORE CLOCK INPUT (HCL     |                        |                                                                     |            |      |      |      |                   |

| Amplitude                 | V <sub>CPP,HCLKI</sub> | Differential ECL                                                    | 1          | 400  | 600  | 800  | mVpp              |

| Common Mode Voltage       | V <sub>CM,HCLKI</sub>  |                                                                     | 1          | -0.8 | -1.5 | -2.0 | V                 |

| Input Resistance          | R <sub>HCLKI</sub>     |                                                                     | 3          | 45   | 50   | 55   | Ω                 |

| Input Capacitance         | CHCLKI                 |                                                                     |            |      |      |      | fF                |

| Maximum Frequency         | F <sub>MAX,HCLKI</sub> |                                                                     | 3          | 1300 |      |      | MHz               |

| Minimum Frequency         | F <sub>MIN,HCLKI</sub> |                                                                     | 3          |      |      | 1    | MHz               |

| CLOCK OUPUT (LCLKOP, I    | LCLKON)                |                                                                     |            |      |      |      |                   |

| Amplitude                 | V <sub>CPP,LCLKO</sub> | Differential LVDS                                                   | 2          | 250  | 350  | 450  | mVpp              |

| Common Mode Voltage       | V <sub>CM,LCLKO</sub>  |                                                                     | 2          | 0.9  | 1.2  | 1.5  | mV                |

| Maximum Frequency         | F <sub>MAX,LCLKO</sub> |                                                                     | 3          | 325  |      |      | MHz               |

| Minimum Frequency         | F <sub>MIN,LCLKO</sub> |                                                                     | 3          |      |      | 0.25 | MHz               |

| DIGITAL INPUTS (DIA<0:11  | >, DIB<0:11>           | , DIC<0:11>, DID<0:11>)                                             | _          |      |      |      |                   |

| Input High Voltage        | VIH                    |                                                                     | 2          | 0.9  |      | VCC  | V                 |

| Input Low Voltage         | VIL                    |                                                                     | 2          | -0.4 |      | 0.4  | V                 |

| Input Resistance          | R <sub>DIN</sub>       |                                                                     |            |      |      |      | Ω                 |

| Setup Time                | t <sub>ST,DTHCK</sub>  | From data input to LCLKO                                            | 3          | 300  |      |      | ps                |

| Hold Time                 | t <sub>HL.DTHCK</sub>  | From LCLKO to data input                                            | 3          | -50  |      |      | ps                |

# **Electrical Specification**

| PARAMETER                    | SYMBOL            | CONDITIONS, NOTE                   | TEST LEVEL | MIN  | ТҮР  | MAX  | UNITS |

|------------------------------|-------------------|------------------------------------|------------|------|------|------|-------|

| TERMINATION (VTT)            |                   |                                    |            |      |      |      |       |

| HCLKI Termination<br>Voltage | VTT               |                                    |            |      | -2.0 |      | V     |

| REFERENCE (VREFA, VRE        | FD)               |                                    |            |      |      |      |       |

| Analog Reference             | VREFA             | Internally generated               | 3          | -1.9 | -2.0 | -2.1 | V     |

| Digital Reference            | VREFD             | Internally generated               | 3          | -1.9 | -2.0 | -2.1 | V     |

| Input Resistance             | R <sub>VREF</sub> | For externally driven VREFA, VREFD | 3          | 500  | 560  | 620  | Ω     |

| POWER SUPPLY                 |                   |                                    |            |      |      |      |       |

| Positive Supply              | VCC               |                                    |            | 3.1  | 3.3  | 3.5  | V     |

| Negative Supply, Analog      | VEEA              |                                    |            | -5.4 | -5.2 | -5.0 | V     |

| Negative Supply, Digital     | VEED              |                                    |            | -5.4 | -5.2 | -5.0 | V     |

| Power Dissipation            | Р                 | Total dissipation                  |            |      | 3300 |      | mW    |

| Power Dissipation            | P <sub>VCC</sub>  | Positive supply                    |            |      | 500  |      | mW    |

| Power Dissipation            | PVEEA             | Negative supply, analog            |            |      | 500  |      | mW    |

| Power Dissipation            |                   |                                    |            |      | 2300 |      | mW    |

| OPERATING RANGE              |                   |                                    |            |      |      |      |       |

| Ambient Temperature          | T <sub>A</sub>    |                                    |            |      |      |      | °C    |

| Junction Temperature         | ΤJ                | 120                                |            |      | °C   |      |       |

## **Test Levels**

| TEST LEVEL | TEST PROCEDURE                                                                  |  |

|------------|---------------------------------------------------------------------------------|--|

| 1          | 100% production tested at $T_A = 25C^{1,2}$                                     |  |

| 2          | Sample tested at $T_A = 25C$ unless other temperature is specified <sup>1</sup> |  |

| 3          | Guaranteed by design and/or characterization testing                            |  |

<sup>1</sup> All tests are continuous, not pulsed. Therefore, Tj (junction temperature) > Tc (case temperature) > Ta (ambient temperature). This is the normal operating condition and is more stressful than a pulsed test condition.

$^2~$  The tests are conducted with the power set to  $\text{VCC}_{\text{MIN}}$  and to  $\text{VCC}_{\text{MAX}}.$

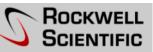

## **Pin Description**

| P/I/O | PIN                                            | NUM. | NAME      | FUNCTION                                                    |

|-------|------------------------------------------------|------|-----------|-------------------------------------------------------------|

| Р     | 7, 16, 39, 62                                  | 4    | VCC       | +3.3V Digital Power Supply                                  |

| Р     | 1, 68, 71, 72, 73, 74, 75, 76, 77              | 9    | VEEA      | -5.2V Analog Power Supply                                   |

| Р     | 10, 14, 26, 52, 64, 67                         | 6    | VEED      | -5.2V Digital Power Supply                                  |

| Р     | Bottom Plate                                   | -    | GND       | Ground                                                      |

| I     | 2                                              | 1    | VREFA     | -2V Reference Voltage                                       |

| I     | 12                                             | 1    | VREFD     | Digital Circuitry Bias Reference. Bypass to Ground          |

| I     | 4                                              | 1    | VTT       | HCLKI Clock Termination Voltage                             |

| I     | 6                                              | 1    | MXM       | Mux Mode Selection: Float – 4:1<br>GND – 2:1                |

| 1     | 5                                              | 1    | HCLKIP    | Clock Input                                                 |

| I     | 3                                              | 1    | HCLKIN    | Clock Input                                                 |

| I     | 8                                              | 1    | LCLKOP    | Low Clock Output                                            |

| I     | 9                                              | 1    | LCLKON    |                                                             |

| I     | 11, 13, 15, 17, 18, 19, 20, 21, 22, 23, 24, 25 | 12   | DIA<0:11> | DIA <i> Is Channel A Digital Bit i Input. MSB is bit 11</i> |

| 1     | 27, 28, 29, 30, 31, 32, 33, 34, 35, 36, 37, 38 | 12   | DIB<0:11> | DIB <i> Is Channel B Digital Bit i Input. MSB is bit 11</i> |

| I     | 51, 50, 49, 48, 47, 46, 45, 44, 43, 42, 41, 40 | 12   | DIC<0:11> | DIC <i> Is Channel C Digital Bit i Input. MSB is bit 11</i> |

| I     | 66, 65, 63, 61, 60, 59, 58, 57, 56, 55, 54, 53 | 12   | DID<0:11> | DID <i> Is Channel D Digital Bit i Input. MSB is bit 11</i> |

| 0     | 70                                             | 1    | OUTP      | Differential Output                                         |

| 0     | 69                                             | 1    | OUTN      |                                                             |

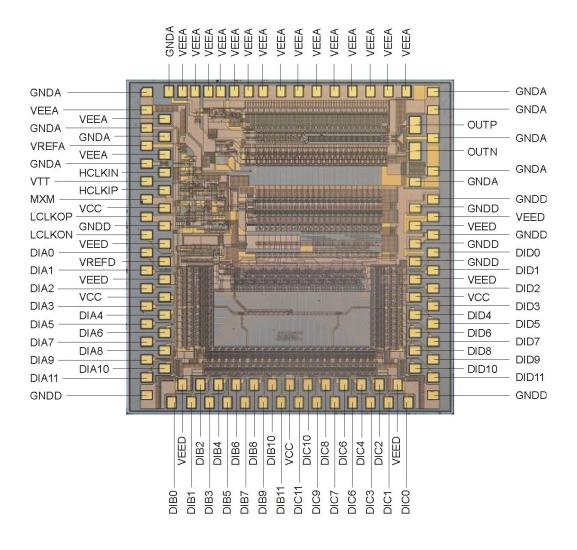

## Pin Layout (TOP view)

Figure 2 - RDA012M4-HD pinout (top view).

# Pad Layout

Figure 3 - RDA012M4 pad layout.

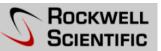

## Theory of Operation

For best dynamic and static performance, the DAC employs 6-bit segmentation. The 3.3V NMOS compatible 12-bit digital data inputs are latched by a master-slave flip-flop immediately after the input buffer to reduce the data skew. The four-channel data are combined together by the 48:12 MUX and latched again. The 6 MSB data bits are decoded into thermometer code by a two-stage decoding block, and the 6 LSB data bits are transported through the delay equalizer block. The digital data are synchronized again by a second master slave flip-flop to reduce the switching glitch. The decoded 6 MSB data drive 63 identical current switches, and the 6 LSB data drive 6 current switches. The output nodes from the LSB current switches are connected to the analog output through an R-2R ladder to generate the binary output.

The DAC output full-scale voltage follows the relationship  $V_{FS} = 0.3 x V_{REF.}$  An internal reference circuit with approximately -10dB

supply rejection is integrated on chip for application convenience. The reference pin is provided for monitoring and for bypass purposes. To band-limit the noise on the reference voltage, the reference pin should be bypassed to the GNDA node with capacitance > 100pF. The VREF pin can also be used to override the internal reference with an accurate, temperature-compensated external voltage reference.

The timing diagram is shown in figure 3. The 1.3GHz external clock (HCLKI) is divided by 2 and 4 resulting in the MUX internal selection signals S0 and S1. A low-speed clock (LCLKO) is provided to drive the external digital. The four-channel data input are latched with an internal clock that is synchronized with the LCLKO. Controlled by S0 and S1, input data are fed to the 1.3GS/s DAC in the order shown.

Figure 4 - Input Timing Diagram.

## Signal Description

#### HIGH SPEED INPUT CLOCK.

The RDA012M4 high-speed clock input is differential and can be driven from typical ECL circuits. Also a differential sinusoidal clock can be used. The HCLKIP and HCLKIN inputs, are internally terminated with 50  $\Omega$  to VTT which should be connected to a well decoupled –2.0 volt supply. Since the MUXDAC's output phase noise is directly related to the input clock noise and jitter, a low-jitter clock source is ideal. The internal clock driver generates very little added jitter (~100fs). A 500MHz MUXDAC output demands a white noise induced clock jitter of less than 250fs for a 10-bit equivalent, 62dB SNDR.

#### DATA INPUT.

The data inputs are 3.3V NMOS-compatible. The data is interleaved according to significant bit. For example, consecutive data pins will occur as DIA0, DIB0, DIC0, DID0, DIA1, DIB1, etc.

#### OUTPUT CLOCK.

Output clock LCLKOP and LCLKON are supplied for the DSP/FPGA/ASIC. They are LVDS compliant and needs to be terminated with a  $100\Omega$  resistor in front of the receiving buffer or the receiving pins of the ASIC/DSP.

For application convenience, the data input's setup and hold time is specified with respect to the LCLKO. It should be noted that LCLKOP and LCLKON are driven by the MUXDAC and the waveforms of these signals are better defined at the receiver end; that is, near the ASIC/DSP chip that provides the input data for the MUXDAC. The system designer should consider the delay associated with the signal routing in the system's timing budget.

In figure 6, the setup and hold time of the LCLK to data transition are defined at the MUXDAC side. Data transitions of the data input have to occur during the "Valid Data Transition Window." The timing margin seen from the MUXDAC is  $T_P$ - $T_S$  where  $T_P$  is the LCLKO period and  $T_S$  is the setup time, assuming that the ASIC chip takes LCLKO as the clock input and its outputs are latched at the falling edge of the clock.

From the ASIC/DSP end, however, the timing margin is decreased by the amount equal to the sum of the data delay and clock delay between the two chips, as noted in the lower part of the diagram.

#### ANALOG OUTPUT.

The outputs OUTP and OUTN should both be connected though a 50  $\Omega$  resistor to ground. This will give a full-scale amplitude of 0.6 volt (both outputs must be terminated), 1.2 volt differentially. The output common mode can be changed by terminating the load resistors to a different voltage. However, the device is optimized to perform best when connected to a voltage between 0 and 1 volt. For reliable operation, the output termination voltage should not exceed 3 volts.

#### REFERENCE.

VREFA is provided for added control of the fullscale amplitude output. The internal reference circuit is designed to provide -2.0 volts, which can change up to  $\pm 5\%$  as the supply voltage and/or operating temperature changes. If the user prefers accurately control the output fullscale signal, an external voltage reference with low output impedance to override the internal reference should be used. The output full-scale voltage follows the relationship  $V_{FS} = 0.3 x V_{REF}$ . Note that the MUXDAC is optimized to have the best performance with a reference voltage of -2.0 volts. The output resistance of the reference node is 560  $\Omega$  ±10%. VREFD allows adjusting of the digital circuitry bias point for varying input voltage swings. In most cases, VREFD should be bypassed to GND.

# **Typical Operating Circuit**

Figure 5 - RDA012M4 typical operating circuit using the internal voltage reference.

# **Typical Performance**

Figure 8 - Output spectrum at Fclk=1300MHz, Fout=340MHz

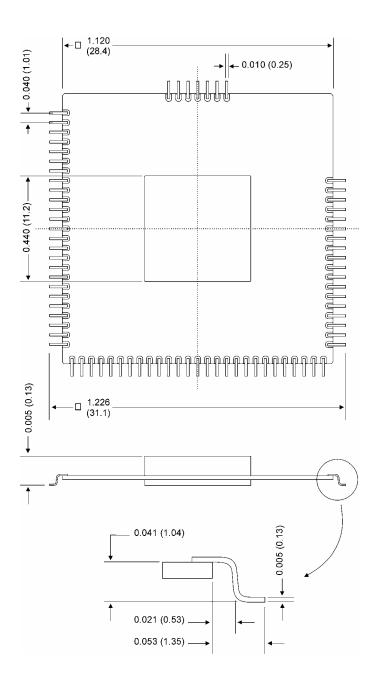

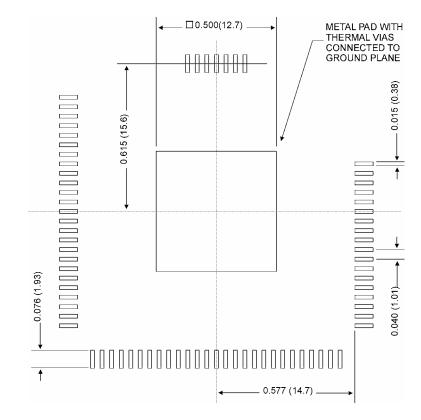

# Package Information

The package is a 77 pin HSD with a heat sink slug on the package's bottom. The leads are gull-winged formed and trimmed to 0.053 inch (1.35 mm) in lenght.

Figure 9 - RDA012M4-HD package, dimensions shown in inches (mm).

Figure 10 - RDA012M4-HD footprint, dimensions shown in inches (mm).